目录

TLC5940 是一款16通道恒流LED驱动器,具有亮度校正和灰度PWM控制。以下是其主要特点和应用介绍:

特点

-

16通道驱动:每个通道都能够独立驱动LED灯。

-

12位灰度PWM控制:提供4096级的亮度控制,使LED灯能够实现平滑的亮度变化。

-

亮度校正:

- 提供6位(64级)的亮度校正,调整各LED通道之间及其他LED驱动器之间的亮度差异。

- 校正数据可以存储在集成的EEPROM中。

-

驱动能力(恒流吸入):

- 在VCC < 3.6 V时,电流范围为0 mA到60 mA。

- 在VCC > 3.6 V时,电流范围为0 mA到120 mA。

-

LED供电电压:支持最高17 V的电压。

-

电源电压范围:VCC可以在3 V到5.5 V之间。

-

串行数据接口:通过串行接口访问灰度控制和亮度校正。

-

错误信息检测:

- LED开路检测(LOD):检测输出端子上的断开或未连接的LED。

- 热错误标志(TEF):指示过温状态。

-

受控的浪涌电流:在启动时限制浪涌电流。

-

30 MHz的数据传输率:支持高速的数据传输。

-

CMOS电平输入/输出:兼容CMOS电平信号。

应用

- 单色、多色、全彩LED显示屏

- LED标牌

- 显示器背光

- 通用高电流LED驱动

TLC5940非常适合需要高精度亮度控制和可靠性的LED驱动应用。它的错误检测功能和亮度校正能力使其在复杂的LED显示系统中表现出色。

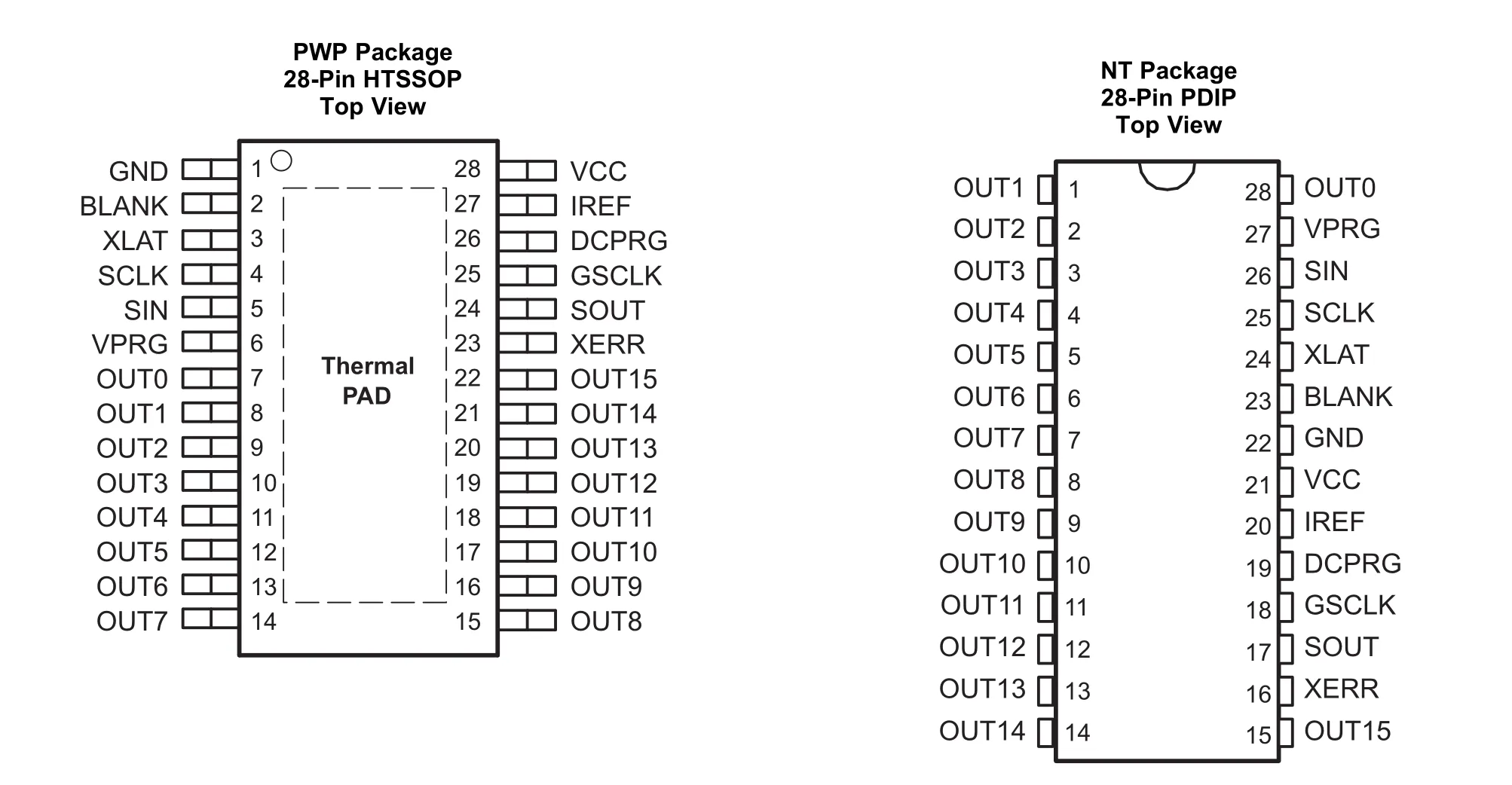

| PIN | TYPE | DESCRIPTION |

|---|---|---|

| BLANK | I | 清空所有输出。当BLANK = H时,所有OUTn输出被强制关闭。GS计数器也会被重置。当BLANK = L时,OUTn由灰度PWM控制。 |

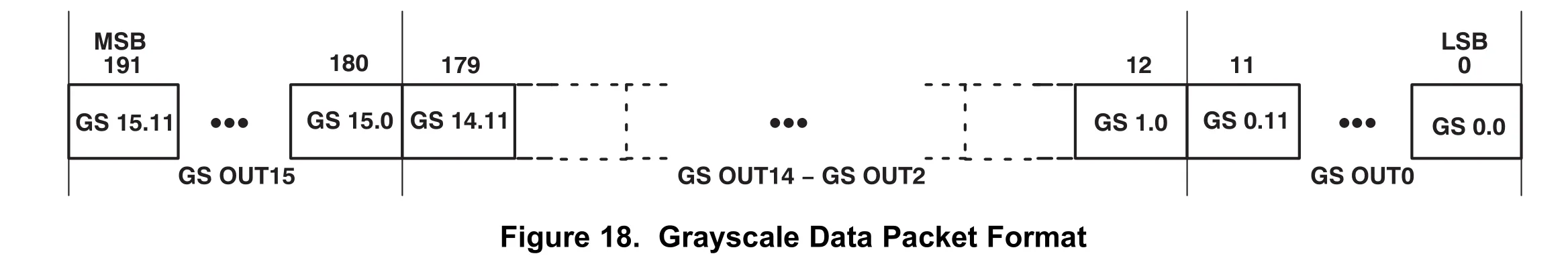

| DCPRG | I | 开关DC数据输入。当DCPRG = L时,DC连接到EEPROM。当DCPRG = H时,DC连接到DC寄存器。DCPRG还控制EEPROM写入,当VPRG = V (PRG)时。默认EEPROM数据为3Fh。 |

| GND | G | 地(接地) |

| GSCLK | I | 灰度PWM控制的参考时钟。 |

| IREF | I | 参考电流端口。 |

| NC | — | 无连接 |

| OUT0 | O | 恒定电流输出 |

| OUT1 | O | 恒定电流输出 |

| OUT2 | O | 恒定电流输出 |

| OUT3 | O | 恒定电流输出 |

| OUT4 | O | 恒定电流输出 |

| OUT5 | O | 恒定电流输出 |

| OUT6 | O | 恒定电流输出 |

| OUT7 | O | 恒定电流输出 |

| OUT8 | O | 恒定电流输出 |

| OUT9 | O | 恒定电流输出 |

| OUT10 | O | 恒定电流输出 |

| OUT11 | O | 恒定电流输出 |

| OUT12 | O | 恒定电流输出 |

| OUT13 | O | 恒定电流输出 |

| OUT14 | O | 恒定电流输出 |

| OUT15 | O | 恒定电流输出 |

| SCLK | I | 串行数据移位时钟 |

| SIN | I | 串行数据输入 |

| SOUT | O | 串行数据输出 |

| VCC | I | 电源电压 |

| VPRG | I | 多功能输入端口。当VPRG = GND时,设备处于GS模式。当VPRG = VCC时,设备处于DC模式。当VPRG = V时,DC寄存器数据可以通过DCPRG = HIGH编程到DC EEPROM中。默认EEPROM数据为3Fh。 |

| XERR | O | 错误输出。XERR是一个开漏端口。XERR在检测到LOD或TEF时为低电平。 |

| XLAT | I | 电平触发锁存信号。当XLAT为高时,TLC5940会将数据从输入移位寄存器写入GS寄存器(VPRG = 低)或DC寄存器(VPRG = 高)。当XLAT为低时,GS或DC寄存器中的数据保持不变。 |

8.3 功能描述

8.3.1 串行接口

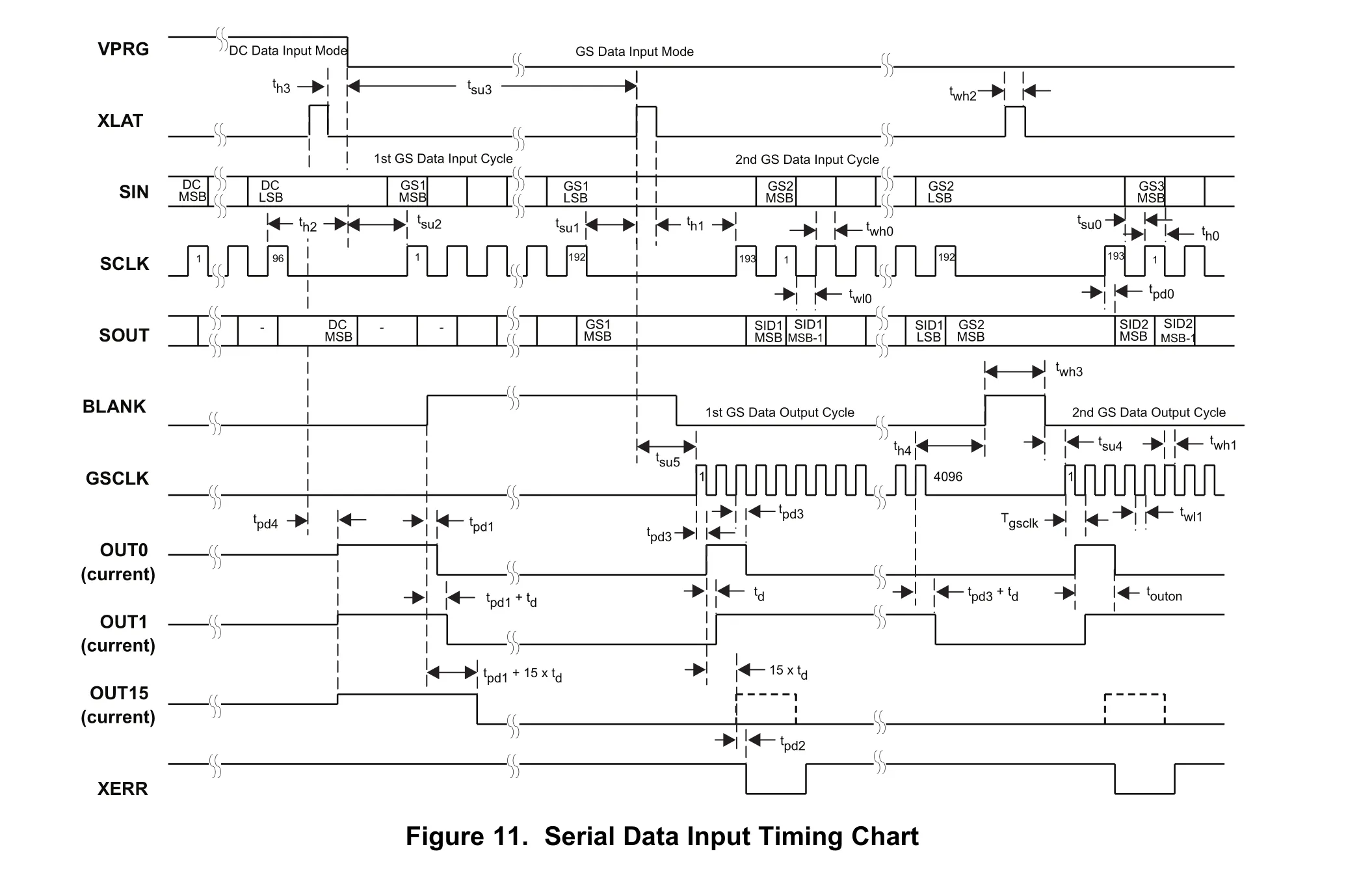

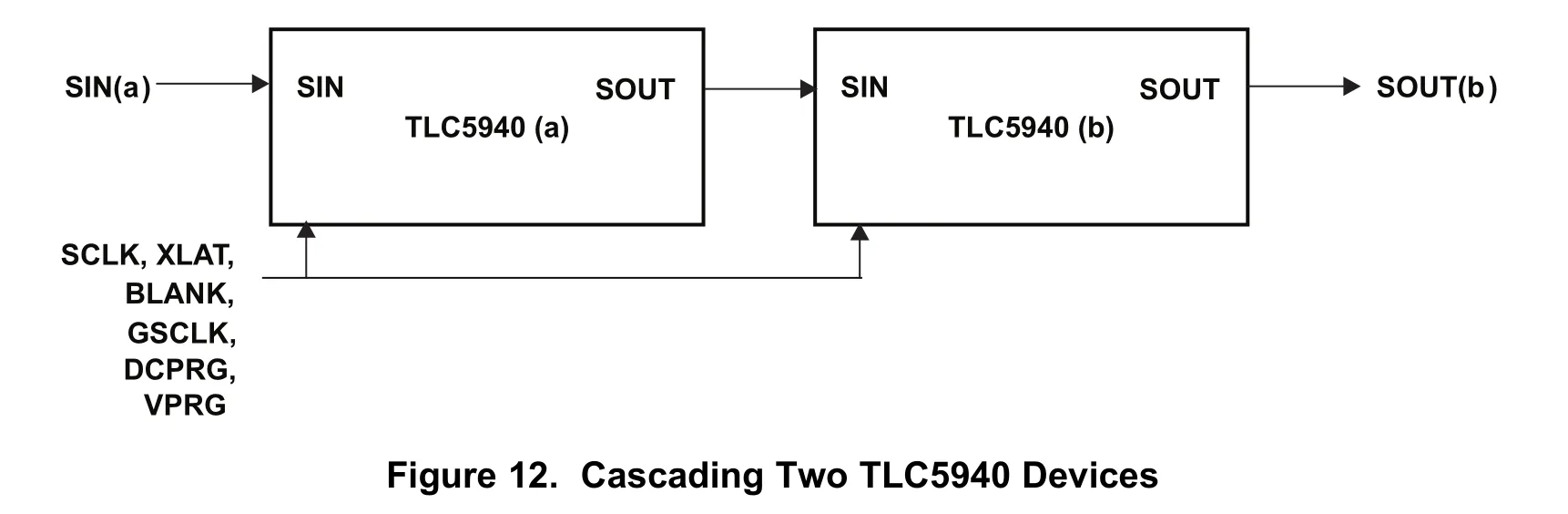

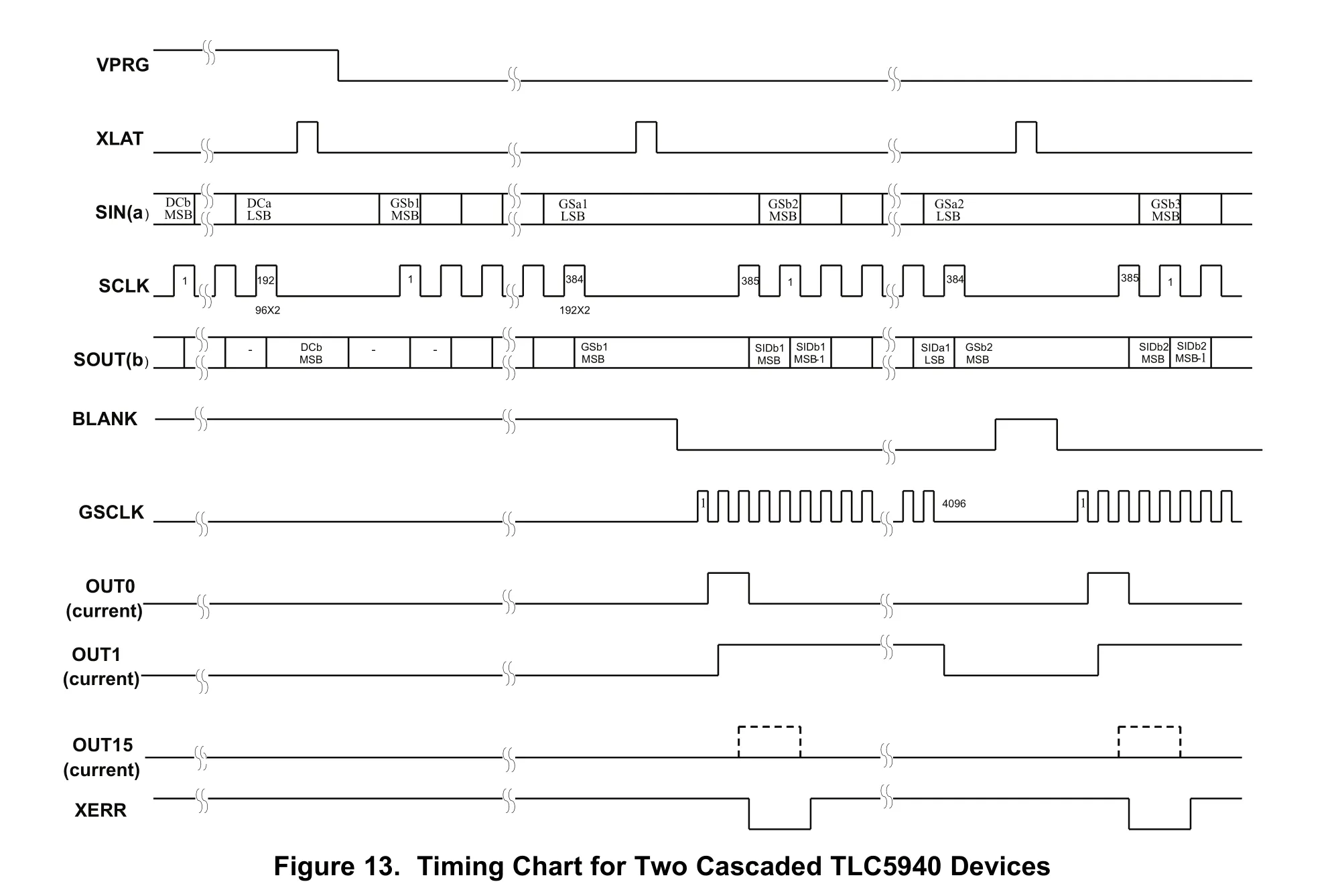

TLC5940 具有灵活的串行接口,可以通过多种方式与微控制器或数字信号处理器连接。只需 3 个引脚即可将数据输入到设备中。SCLK 信号的上升沿将数据从 SIN 引脚移至内部寄存器。在所有数据都被时钟输入之后,XLAT 信号的高电平脉冲会将串行数据锁存到内部寄存器中。内部寄存器是由 XLAT 信号触发的电平锁存器。所有数据按 MSB(最有效位)优先的顺序被时钟输入。串行数据的长度为 96 位或 192 位,具体取决于编程模式。灰度数据和点校正数据可以在灰度周期中输入。尽管新的灰度数据可以在灰度周期中时钟输入,但 XLAT 信号应仅在灰度周期结束时锁存灰度数据。立即锁存新的灰度数据会覆盖现有的灰度数据。图 11 显示了时序图。可以通过将一个设备的 SOUT 引脚连接到下一个设备的 SIN 引脚,来串联连接多个 TLC5940 设备。图 12 显示了级联两个 TLC5940 的示例,时序图见图 13。SOUT 引脚也可以连接到控制器,以接收来自 TLC5940 的状态信息,如图 22 所示。

8.3.2 错误信息输出

开漏输出 XERR 用于报告 TLC5940 的两个错误标志:TEF(溢出错误标志)和 LOD(低电平检测错误标志)。在正常工作条件下,连接到 XERR 引脚的内部晶体管是关闭的,XERR 上的电压通过外部上拉电阻被拉高至 VCC。如果检测到 TEF 或 LOD 错误,内部晶体管会被打开,XERR 被拉低至 GND。由于 XERR 是一个开漏输出,多个 IC 可以通过逻辑“或”连接在一起,并通过一个单独的上拉电阻拉高至 VCC。这减少了报告系统错误所需的信号数量(参见图 22)。

为了区分 XERR 引脚上的 LOD 和 TEF 信号,可以通过将 BLANK 设置为 HIGH 来屏蔽 LOD。

8.3.3 TEF: 热错误标志

TLC5940 提供了一个温度错误标志(TEF)电路,用于指示 IC 的过温状态。如果结温超过阈值温度(典型值为 160°C),TEF 会变为高电平(H),同时 XERR 引脚会拉低至低电平。 当结温低于阈值温度时,TEF 会变为低电平(L),XERR 引脚则变为高阻态。TEF 状态也可以从 TLC5940 的状态寄存器中读取。

8.3.4 LOD: LED 开路检测

TLC5940 具有 LED 开路检测器,用于检测断开或断开的 LED。当检测到 LED 开路时,LED 开路检测器会将 XERR 引脚拉低至 GND。只有在以下开路 LED 条件下,XERR 和状态信息数据中的相应错误位才会被激活:

- OUTn 引脚开启,并且经过了延迟时间 tpd2(典型值为 1 μs)。

- OUTn 的电压 < 0.3 V(典型值)。

每个输出的 LOD 状态也可以从 SOUT 引脚读取。有关详细信息,请参见“状态信息输出”部分。当 XLAT 从高电平返回到低电平时,LOD 错误位会被锁存到状态信息数据中。因此,当 XERR 激活时,XLAT 引脚必须进行一次高低脉冲操作,以将 LOD 错误锁存到状态信息数据中,供后续通过串行移位寄存器读取。

8.3.5 输出间延迟

TLC5940 在输出之间有逐级延迟电路。这些电路位于设备的恒流驱动块中(参见功能块图)。固定的延迟时间为 20 ns(典型值),OUT0 没有延迟,OUT1 延迟 20 ns,OUT2 延迟 40 ns,依此类推。最大延迟为从 OUT0 到 OUT15 之间的 300 ns。该延迟在每个输出通道的开关操作时工作,这些延迟有助于防止大电流冲击,从而减少输出开启时旁路电容的需求。

8.3.6 输出使能

TLC5940 的所有 OUTn 通道可以通过一个信号关闭。当 BLANK 引脚设置为高电平时,所有 OUTn 通道都会被禁用,无论设备的逻辑操作如何。同时,灰度计数器也会被重置。当 BLANK 引脚设置为低电平时,所有 OUTn 通道在正常条件下工作。如果 BLANK 引脚先下降再回升,并且回升的时间少于 300 ns,那么所有被编程为开启的输出仍然会开启,开启时间为编程的灰度时钟数或 BLANK 信号低电平时长(取较小者)。例如,如果所有输出被编程为开启 1 毫秒,但 BLANK 信号仅为低电平 200 ns,则所有输出仍然会开启 200 ns,即使有些输出在 BLANK 信号已经回升后才开启。

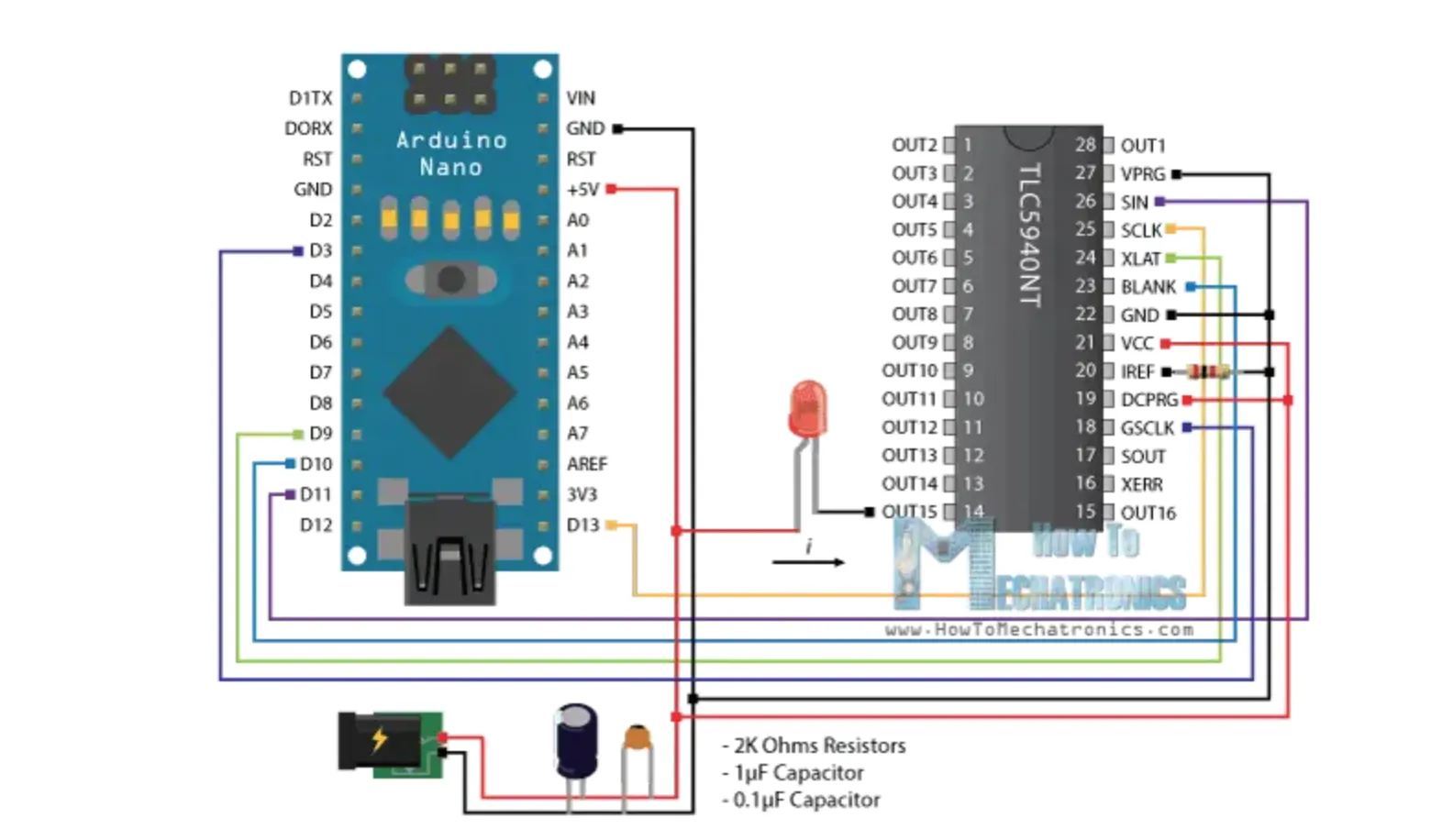

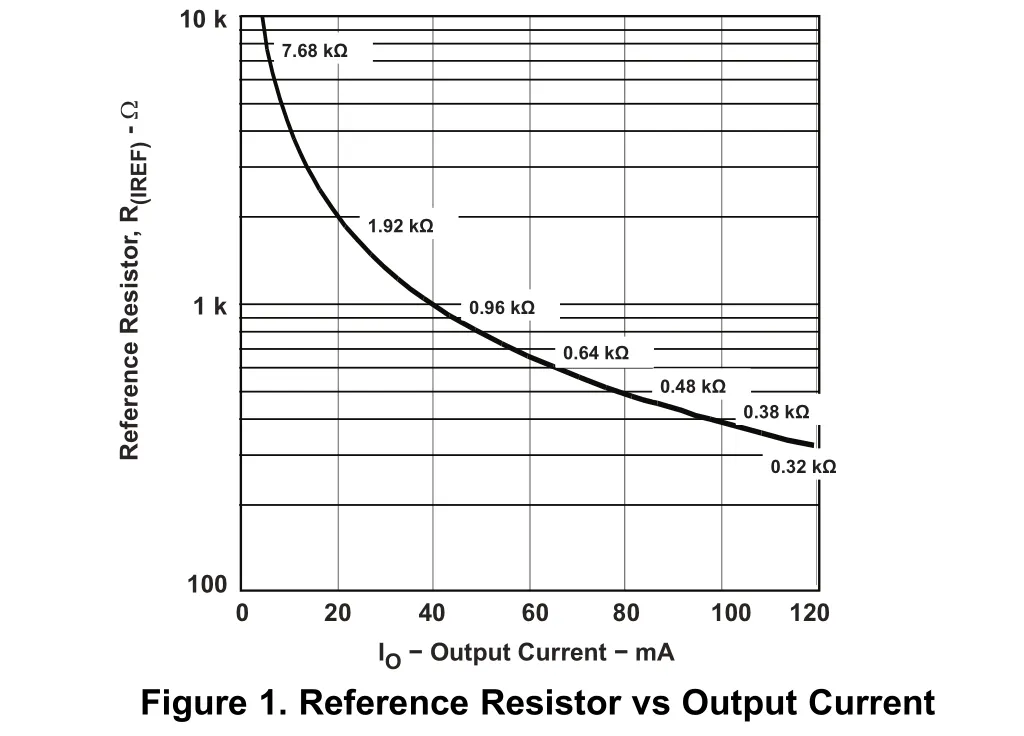

设置最大通道电流

每个通道的最大输出电流通过一个单独的电阻 R (IREF) 来编程,该电阻连接在 IREF 引脚和 GND 引脚之间。IREF 引脚上的电压由一个内部带隙参考电压 V (IREF) 设置,典型值为 1.24 V。最大通道电流等于流过电阻 R (IREF) 的电流乘以一个系数 31.5。每个通道的最大输出电流可以通过公式 6 计算。

其中:

• V (IREF) = 1.24 V

• R (IREF) = 用户选择的外部电阻

I_max 必须设置在 5 mA 和 120 mA 之间。如果 I_max 设置低于 5 mA,输出电流可能会不稳定。通过将 I_max 设置为 5 mA 或更高,然后使用点校正,可以实现低于 5 mA 的输出电流。

图 1 显示了最大输出电流 I_O 与电阻 R (IREF) 之间的关系。R (IREF) 是连接 IREF 引脚和 GND 的电阻值,I_O 是从 OUT0 到 OUT15 的恒定输出电流。可以通过电阻将可调电源连接到 IREF 引脚,从而改变每个通道的最大输出电流。每个通道的最大输出电流是流出 IREF 引脚的电流的 31.5 倍。

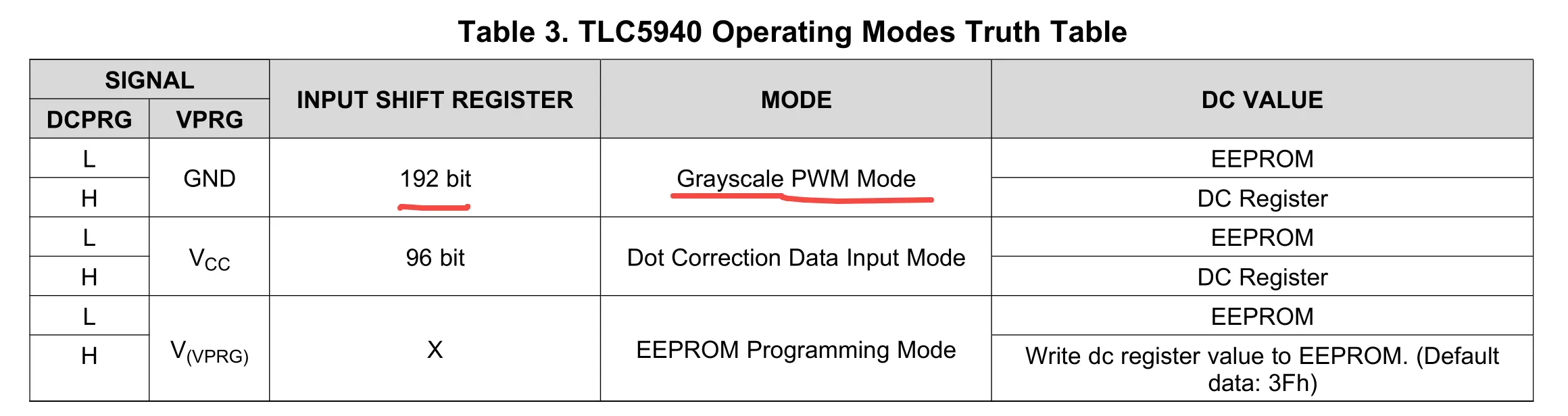

8.4 设备功能模式

8.4.1 操作模式

TLC5940的操作模式取决于信号DCPRG和VPRG。表3显示了可用的操作模式。TPS5940的GS操作模式(参见图11)和移位寄存器的值在上电后未定义。为了解决这个问题,可以在TLC5940上电后设置点修正数据,然后切换回GS PWM模式。另一种解决方法是将输入移位寄存器溢出,填充193位的虚拟数据并在TLS540处于GS PWM模式时锁存它。上电后,输入移位寄存器、DC寄存器和GS寄存器的值是未知的。应通过串行接口在开始操作前适当地存储DC和GS寄存器的值。

8.4.2 设置点修正(DOT Correction)

TLC5940具有独立微调每个通道(OUT0到OUT15)输出电流的能力,这称为点修正(Dot Correction)。此功能用于调整连接到输出通道OUT0至OUT15的LED的亮度偏差。每个16个通道都可以通过一个6位的字进行编程。通道输出可以在64个步骤之间调整,从0%到最大输出电流 ( I_{\text{max}} ) 的100%。所有通道的点修正数据必须同时输入。

输出电流 ( I_n ) 的计算公式如下:

其中:

- 为每个输出的最大可编程输出电流。

- 为输出n的编程点修正值 的范围为 0 到 63)。

- 为0到15。

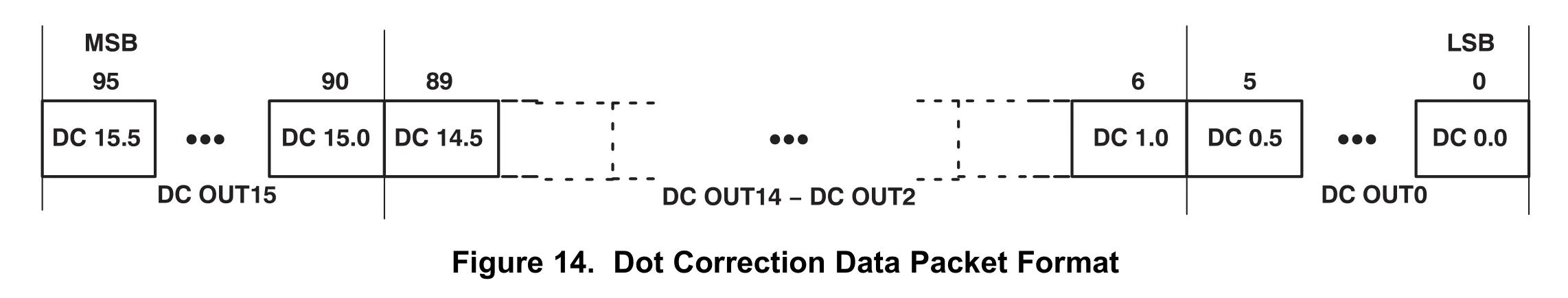

图14展示了点修正数据包的格式,其中包含6位x16个通道,总计96位。该格式为大端格式(Big-Endian),即最高有效位(MSB)首先传输,其次是次高有效位(MSB-1),依此类推。图14中的DC15.5代表输出15的第5位有效位。

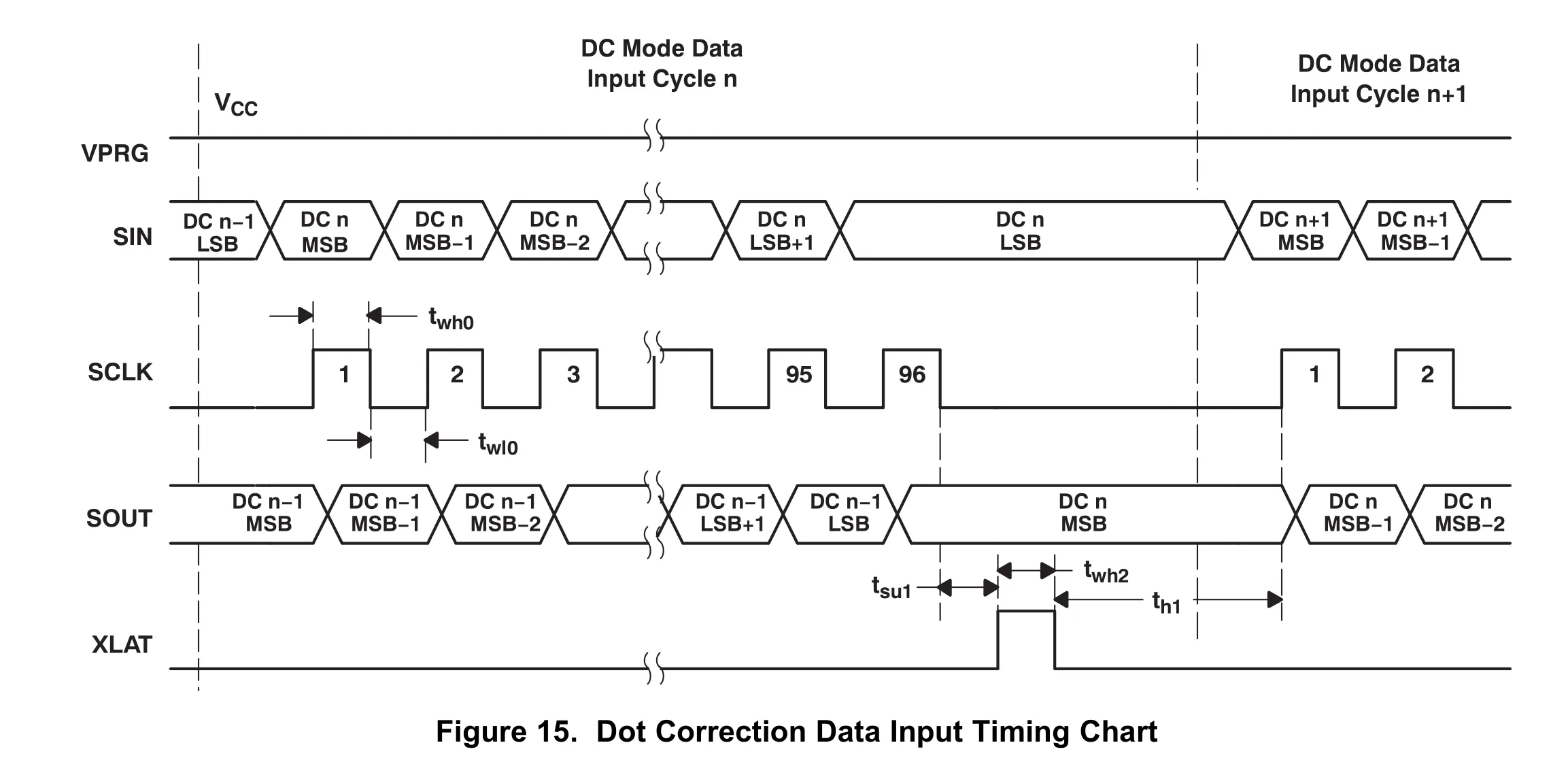

当VPRG设为VCC时,TLC5940进入点修正数据输入模式。此时,输入移位寄存器的长度为96位。所有串行数据移入后,当XLAT为高电平时,TLC5940将输入移位寄存器中的数据写入DC寄存器;当XLAT为低电平时,DC寄存器中的数据保持不变。DC寄存器是一个由XLAT信号触发的电平锁存器。由于XLAT是电平触发信号,因此在XLAT为高电平时,SCLK和SIN信号不能发生变化。XLAT变为低电平后,DC寄存器中的数据被锁存,并且不会发生变化。BLANK信号不需要为高电平才能锁存新数据。XLAT有设置时间(tsu1)和保持时间(th1),这些参数与SCLK的关系如图15所示。

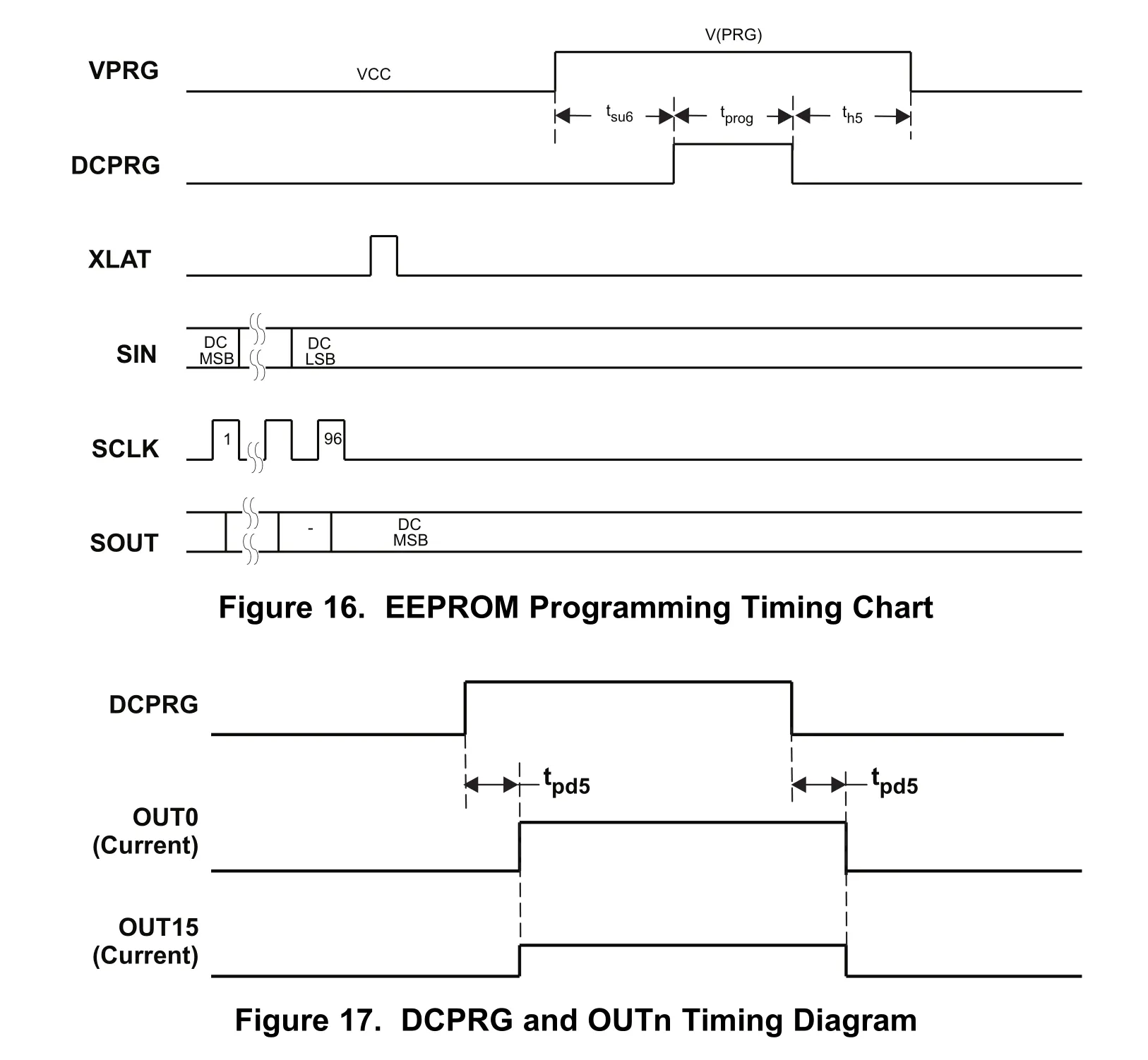

TLC5940还具有一个EEPROM,用于存储点修正数据。为了将点修正寄存器中的数据存储到EEPROM中,需要在将VPRG信号应用到VPRG引脚后,将DCPRG设为高电平。图16展示了EEPROM编程的时序。EEPROM的默认值为全1。

8.4.3 设置灰度(Grayscale)

TLC5940可以使用PWM控制方案调整每个通道OUTn的亮度。每个通道使用12位表示,结果提供4096个不同的亮度步骤,范围从0%到100%的亮度。公式8用于确定每个输出n的亮度级别:

其中:

- ( \text{GSn} ) 为输出n的编程灰度值(( \text{GSn} ) 的范围是 0 到 4095)。

- ( n ) 为 0 到 15(对应16个通道)。

- 灰度数据适用于所有OUTn。

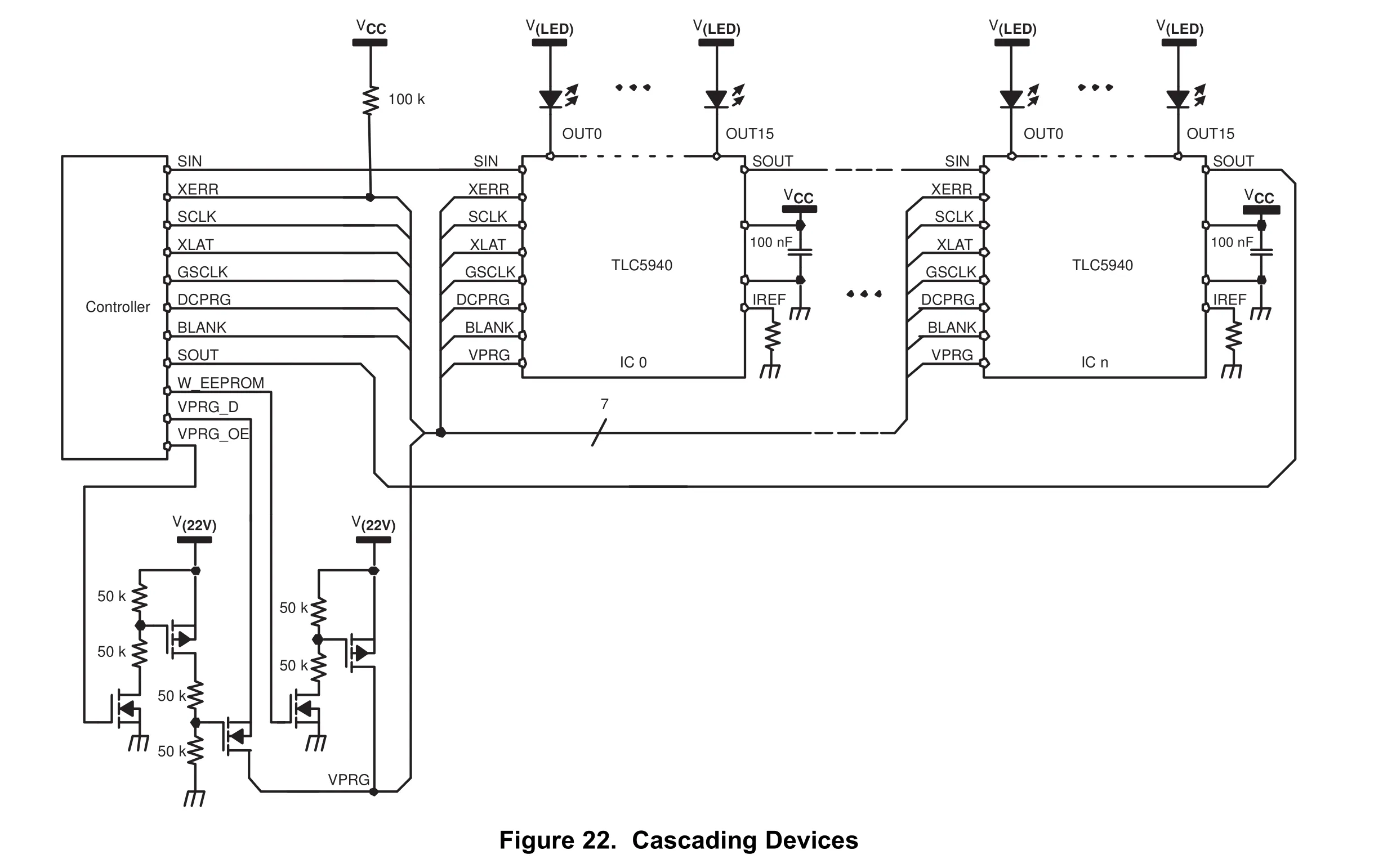

图18展示了灰度数据包的格式,包含12位x16个通道,总计192位。该格式为大端格式(Big-Endian),即最高有效位(MSB)首先传输,接着是次高有效位(MSB-1),依此类推。

当VPRG设置为GND时,TLC5940进入灰度数据输入模式。设备将输入移位寄存器切换为192位宽度。所有数据通过时钟输入后,XLAT信号的上升沿将数据锁存到灰度寄存器(见图11)。新的灰度数据将在XLAT信号的上升沿立即生效;因此,新的灰度数据应在灰度周期结束时锁存,当BLANK为高电平时。点修正之后的第一次GS数据输入周期需要在XLAT信号之后额外提供一个SCLK脉冲来完成灰度更新周期。所有在输入移位寄存器中的GS数据会在更新灰度寄存器后被状态信息数据(SID)替换。

8.4.4 状态信息输出

TLC5940具有一个状态信息寄存器,在灰度模式下(VPRG=GND)可以访问。在XLAT信号将数据锁存到GS寄存器后,输入移位寄存器中的数据将被设备的状态信息数据(SID)替换(见图18)。可以从SOUT引脚读取LOD、TEF以及点修正EEPROM数据(当DCPRG=LOW时)或点修正寄存器数据(当DCPRG=HIGH时)。状态信息数据包为192位宽。位0-15包含每个通道的LOD状态,位16包含TEF状态。如果DCPRG为低电平,位24-119包含点修正EEPROM的数据。如果DCPRG为高电平,位24-119则包含点修正寄存器的数据。剩余的位被保留。完整的状态信息数据包如图19所示。

SOUT在SID寄存器存储SID数据的同时输出SID的MSB,如图20所示。接下来的SCLK脉冲(用于接收下一个灰度数据的SMB时钟)将传输SID的MSB-1。如果输出电压低于0.3V(典型值),并且输出下沉电流开启,则LOD状态标志变为活动状态。LOD状态标志是一个内部信号,当该标志变为活动状态时,它会将XERR引脚拉低。延迟时间tpd2(最大1μs)是从下沉电流开启到LOD状态标志变为有效的时间。每个通道的LOD状态有效时间由30ns(最大值)的通道间开关时间偏移。首次GSCLK上升沿后,OUT0的LOD状态有效;tpd3 + tpd2 = 60ns + 1μs。OUT1的LOD状态有效;tpd3 + td + tpd2 = 60ns + 30ns + 1μs = 1.09μs。OUT2的LOD状态有效;tpd3 + 2td + tpd2 = 1.12μs,以此类推。从首次GSCLK上升沿开始,最多需要1.51μs(tpd3 + 15td + tpd2)直到所有LOD状态变为有效;为了确保所有LOD数据有效,tsuLOD必须大于1.51μs(见图20)。

8.4.5 灰度PWM操作

灰度PWM周期从BLANK信号的下降沿开始。BLANK变为低电平后的第一个GSCLK脉冲使灰度计数器加一,并打开所有灰度值不为零的OUTn。之后每个GSCLK脉冲的上升沿都会使灰度计数器加一。TLC5940会将每个输出OUTn的灰度值与灰度计数器的值进行比较。所有灰度值与计数器值相等的OUTn将被关闭。在经过4096个GSCLK脉冲后,BLANK=H信号会将灰度计数器重置为零,并完成一个灰度PWM周期(见图21)。当计数器达到FFFh时,计数器停止计数,所有输出关闭。如果在计数器未达到FFFh之前将BLANK拉高,计数器会立即被重置为零。

应用

本文作者:Dong

本文链接:

版权声明:本博客所有文章除特别声明外,均采用 CC BY-NC。本作品采用《知识共享署名-非商业性使用 4.0 国际许可协议》进行许可。您可以在非商业用途下自由转载和修改,但必须注明出处并提供原作者链接。 许可协议。转载请注明出处!